產業解析:由先進封裝看 Bonder 產業機會與風險

前言

封裝設備年產值約 40 億美元,其中 Bonder 佔比就高達 4 成,可謂最為關鍵的封裝設備。Bonder 產業發展雖已近 50 年,但隨著前段製程微縮放緩,先進封裝成為延續摩爾定律的新顯學,為 Bonder 產業注入新成長動能,但對於既有業者既是機會也有風險。在本篇文章,我們將嘗試解析先進封裝發展對於後續 Bonder 技術路線的影響,以及對於相關供應鏈帶來的潛在機會與風險。文章內提及公司將包含:

封裝 Bonder:庫力索法 K&S (KLIC)、ASMPT、BESI、芝浦機電 Shibaura Mechatronics、Hanmi 半導體、三星 SEMES、EVG、SUSS MicroTec、TEL 東京威力科創

HBM:海力士、三星、美光

什麼是 Bonder

為了讓晶片能夠與 PCB 主板上的其他元件互通,會將晶片先與導線架 (Lead Frame) 或載板 (Substrate) 接合並完成封裝,後續再與 PCB 進行接合。其中將晶片先與導線架或載板接合的封裝程序稱為 bonding,而用於 bonding 的設備就稱為 bonder。

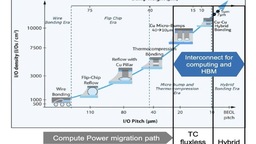

IO Pitch 微縮為推動 Bonder 發展關鍵要素

晶片透過 IO (Input/Output,輸入/輸出) 腳位與載板接合,得以收發電訊號與外部元件溝通,隨著晶片運算能力越趨強大複雜,所需訊號傳輸 IO 數量自然愈多。而 IO 腳位之間的間距 (Pitch) 越小,相同晶片面積所能容納的 IO 數量自然越高,因此 IO Pitch 微縮成為推動封裝 Bonder 發展的關鍵要素。

1970~1990 年代:Wire bonder 為主流

在半導體發展初期,IO 數量要求低,尚未完成封裝的裸晶 (Die) 主要是透過金屬導線與導線架接腳接合,此種接合稱為打線接合 Wire bonding。Wire bonding 適用於 IO Pitch 在 150~200μm 以上的低階成熟應用,但由於發展成熟可靠性高、成本低,因此仍在 NAND flash、DRAM、低階消費性、車用、工業半導體市場廣泛應用。

Wire bonder 為產值最高的 bonder 類別,近 10 年產值在 6~17 億美元波動,排除疫情不正常拉貨高峰則平均約在 8 億美元左右,主要業者為庫力索法 K&S、ASMPT。

1990~2010:Flip Chip bonder 走進主流

隨著對更高 IO 腳位需求,Wire bonding 逐漸不符合所需。在 IBM 的推動下,覆晶封裝 Flip Chip 快速發展,透過裸晶下方密集凸塊 (bump) 取代位於四周的導線,使得 IO 數量得以大幅提升。Flip Chip 適用於 IO Pitch 在 50~200μm 中高階運算晶片主流應用。

Flip Chip bonder 近年產值估計約在 3 億美元上下,主導業者為 BESI、ASMPT、以及受惠供貨台積電而快速成長芝浦機電 Shibaura Mechatronics。

2010~至今:TC bonder 興起

隨著 IO Pitch 微縮進入 50μm 以內,過往 Flip chip 採用回焊加熱 (Mass Reflow) 開始出現瓶頸:

熱膨脹係數翹起問題:較薄的裸晶和載板在高溫下,會產生翹起 (warpage),導致部分焊球沒有接合的共面性問題

在凸塊縮小下,Mass Reflow 一次大量處理晶片雖然效率高,卻可能導致不同 Chip 其載板與 Die 接合的垂直高度差異大

晶片位置偏移:Reflow 傳輸過程會使載具振動,Reflow 本身晶片也會偏移。間距越小、晶片尺寸越大,則偏移失效越嚴重

為了解決以上的問題,熱壓接合 TCB (Thermal Compression Bonding) 技術開始興起。相對於 Mass Reflow 針對大量晶片與載板同時加熱,TCB 一次只處理一個晶片載板接合,且晶片與載板採用不同加熱源,大大改進了Mass Reflow 缺點。雖然 TCB 有以上優點,但其成本明顯高於 Flip Chip bonding,因此目前僅適用於 IO 間距 10~80μm 先進封裝應用。

在 HBM、2.5D 先進封裝應用快速成長下,TC bonder 產值 23 年僅約 1.25 億美元,24 年估計翻倍達到 3 億美元,規模直逼已發展 30 年的 Flip-Chip bonder。目前主要業者為 Hanmi 韓美半導體、三星子公司 SEMES、ASMPT、庫力索法 K&S。

2016~至今:Hybrid bonder 嶄露頭角

當 IO Pitch 進一步縮小至 10μm 以內,凸塊焊球將衍生更多問題:

兩相鄰焊球更容易碰觸在一起,形成橋接失效短路

當材料為錫合金的焊球在小到 20μm 後,形狀就難以保持為完整圓球,因此改為在銅柱附著錫合金焊料。隨著 Pitch 微縮焊球繼續縮小,則錫合金與銅柱之間 IMC (Intermetallic Compound) 效應將放大,使得 Solder 機械性質與導電性質會大幅降低。

為了解決焊球帶來的限制,業界轉向發展無需凸塊形成焊球 (bumpless) 的混合鍵合 Hybrid bonding 技術,少了焊球不僅 IO 的間距可進一步所小至 10μm 以內,且晶片垂直堆疊的厚度也得以降低。Hybrid bonding 根據製造流程又可分為兩大類:

Wafer to Wafer:晶圓未切割前直接 bonding,後續再切割為一顆顆晶片。優點為晶圓上的多個晶片一次同時接合產出高,但缺點為必須為完全相同尺寸的晶片才能採用,且也無法在接合前就先剔除有問題晶片,使得後續報廢風險上升。目前已應用於 CIS、NAND Flash 製造。

Die to Wafer:先將晶圓切割為一顆顆裸晶 (Die),剔除有問題晶片後,再逐一進行接合。可適用於尺寸不同的異質晶片接合,且由於先剔除有問題裸晶後才接合,可進一步提升良率,但缺點自然為產出慢。目前在先進邏輯晶片封裝開始導入,台積電 SoIC-X 封裝為主要採用者。

Hybrid bonding 雖然發展時間最晚,但已應用於 CIS、NAND Flash、台積電 SoIC-X 先進封裝,個人估計 24 年產值已達 3~4 億美元。目前 Wafer-to-Wafer Hybrid bonder 主要業者為 EVG、TEL、SUSS MicroTec;Die-to-Wafer Hybrid bonder 主要業者估計為 BESI 與 ASMPT。

Bonder 產業競爭格局與評估重點

若我們將 IO Pitch 在 80μm 或 100μm 視為傳統封裝與先進封裝的分野,傳統封裝市場以 Wire bonder、Flip Chip bonder 為主流;先進封裝由 TC bonder、Hybrid bonder 所主導,兩類市場競爭格局明顯不同。

傳統封裝成長性低,Bonder 業者競爭趨緩格局穩定

Wire bonder 和 Flip Chip bonder 為傳統封裝主流,兩種技術發展都已超過 30 年邁入成熟期,觀察同業之間營收變化,可發現領先業者長期市占率穩定,同業之間競爭趨緩。

Wire bonder 主要業者為庫力索法 K&S 與 ASMPT,兩者合計市占率約 80% 長期寡佔,過去 10 年未有強力新進者挑戰兩者於 wire bonder 中地位。

庫力索法 K&S:長期在 Wire bonder 市占率高達 60~65%

ASMPT:長期在 Wire bonder 市占率估計約 20%

Flip chip bonder 主要業者為 BESI、ASMPT、Shibaura Mechatronics,三者合計市占率約 80%,同樣屬於寡佔型態。

BESI:長期在 Flip chip bonder 市占率約 30%

ASMPT:長期在 Flip chip bonder 市占率約 25~30%

Shibaura:過去十年市占率快速成長,主要是受惠獨家供應台積電 CoWoS 而快速成長,目前市占率個人估計近 20%

如果排除 Shibaura 的 Flip Chip bonder 主要用於台積電先進封裝,我們可發現傳統封裝 Bonder 主要由庫力索法 K&S、ASMPT、BESI 長期把持,三大巨頭合計於傳統封裝 bonder 市占率高達 80%,明顯寡佔。相較於下游封裝 OSAT 業者前五大 - 日月光、Amkor、長電、通富微電、力成合計市占率僅 64%,Bonder 產業集中度高於下游 OSAT,這使得 K&S、ASMPT、BESI 三家業者對於傳統封裝客戶有一定議價能力,其毛利率長期在 40%、50% 以上較高水準,三大 Bonder 業者其營收受單一客戶影響程度也低於先進封裝。

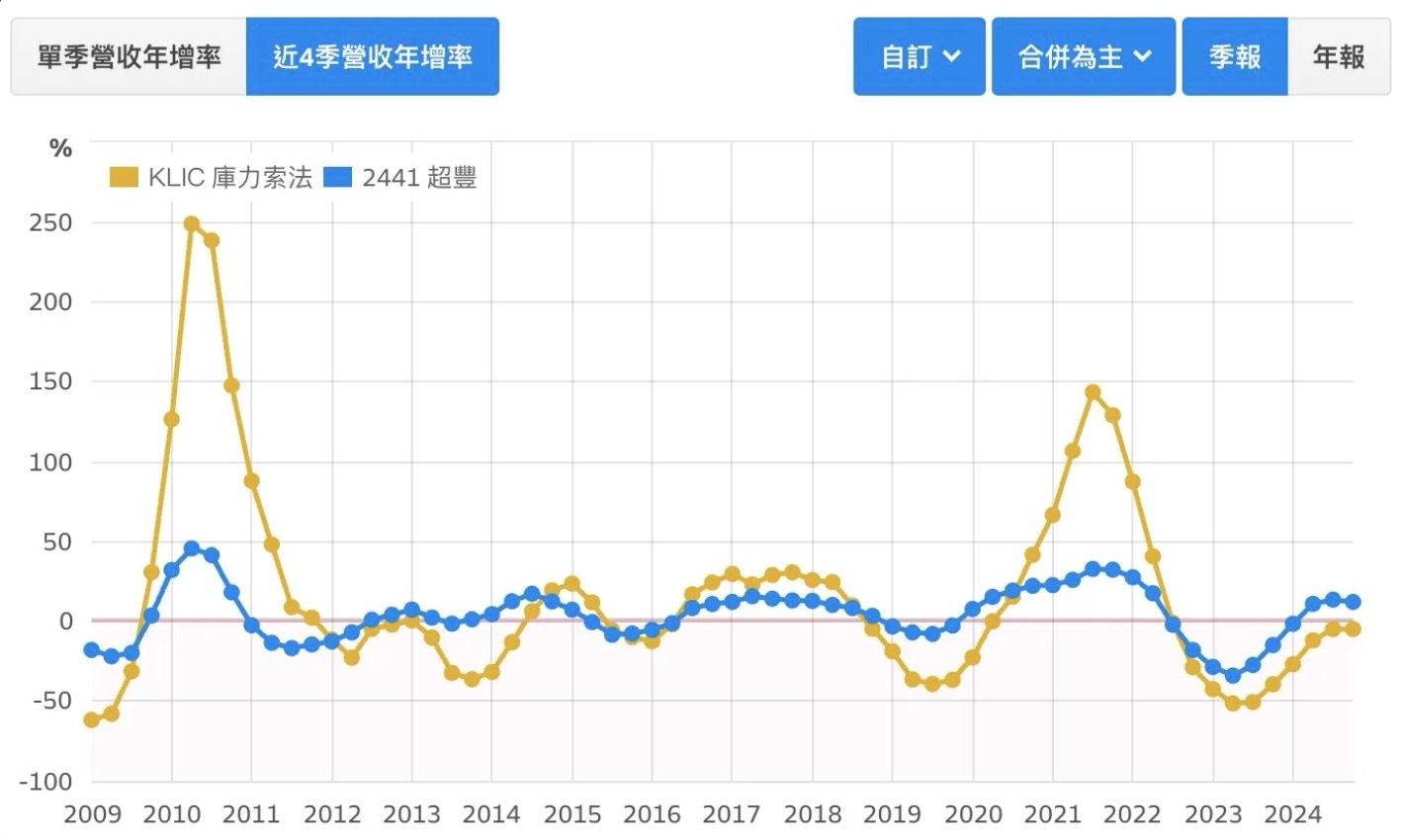

傳統封裝邁入成熟期,成長性隨景氣循環波動明顯

雖然傳統封裝用 Bonder 同業競爭壓力較低,使得庫力索法 K&S、ASMPT、BESI 能享有不錯毛利率,但近十年成長性卻明顯不佳

Wire bonder 2015~2023 年產值沒有成長,維持在 6~7 億美元水準上下

Flip chip bonder 2015~2023 年產值大致上沒有成長

以上顯示:傳統封裝用 Bonder 已走向景氣循環型產業,驅動其產值變化主要因素在於景氣變化。因此投資人在評估傳統封裝用 Bonder 業務展望時,關注重點將在於整體半導體景氣循環處於何種狀態。考量 IC 設計與 IC 封裝族群業績長期為半導體景氣領先指標,我們可以用台股 IC 設計與 IC 封族群營運變化作為傳統封裝用 Bonder 業績展望前瞻。

先進封裝成長性高,但競爭激烈且大客戶極為強勢

先進封裝 Bonder 成長性明顯高於傳統封裝:

TC bonder 產值 23 年僅約 1.25 億美元,24 年估計翻倍為 3 億美元,參考外部研調機構預估 27 年將明顯成長至 9.9 億美元

Hybrid bonder 產值 23 年約 3 億美元,24 年估計成長至 4.2 億美元,參考外部研調機構預估 27 年將成長至 8 億美元

然而高成長也帶來更多競爭,相較於傳統封裝 Bonder 被庫力索法 K&S、ASMPT、BESI 三大業者把持,先進封裝 Bonder 吸引更多新進者投入,同業間市占率變化劇烈。以 TC Bonder 為例,其 2020 年主要供應商為 ASMPT 和 BESI,但 2024 年領先業者個人估計轉變為 Hanmi 韓美半導體、三星 SEMES、ASMPT。

Hanmi:受惠大客戶海力士扶持與快速成長,個人預期市占率快速上升至 40% 以上

三星 SEMES:受惠母公司三星刻意扶持,個人預期市占率快速上升至 30%

ASMPT:早期受惠 Intel 先進封裝需求成長而成為龍頭業者,但隨著 Intel 營運陷入困境短期市占率萎縮至 17~20%

Hybrid bonder 主要業者除了 BESI、ASMPT 等傳統老面孔,更多了 EVG、TEL、SUSS MicroTec 等新興業者,K&S、Shibaura 對此市場也躍躍欲試打算進入。以上皆顯示先進封裝 Bonder 業者之間競爭強度明顯強於傳統封裝,新進者也多於傳統封裝。

大客戶寡佔先進封裝市場,Bonder 業者議價能力明顯弱勢

先進封裝 Bonder 業者市占率變化劇烈,另外一關鍵因素在於下游大客戶對供應鏈強勢主導。不同於傳統封裝下游 OSAT 客戶市占率集中度較為分散,目前先進封裝下游市場則由極少數客戶所把持:

HBM 主要業者為海力士、三星、美光,其中海力士一家市占率 50%

邏輯先進封裝主要業者為台積電、Intel,短期 Intel 營運不佳下台積電市占率一枝獨秀。

先進封裝下游大客戶無論規模、市占率都顯著高於上游 Bonder 業者,這使得大客戶對於上游議價能力極為強勢,具有供應鏈絕對主導權:

海力士基於追求降低成本與地緣政治風險考量下,2017 年起扶植韓國本土業者 Hanmi。在海力士過去 2 年 HBM 營收高速成長下,帶動 Hanmi 於 TC Bonder 市場快速擴大晉升為龍頭。

三星基於追求降低成本與地緣政治風險考量下,扶植自家子公司 SEMES 供應 TC Bonder,24 年估計採購約 100 台,帶動 SEMES 於 TC Bonder 市占率快速上升

台積電於邏輯先進封裝具備獨占地位,帶動 Shibaura 於 fine pitch Flip-Chip bonder 市占率快速成長;但隨著後續 CoWoS-L 轉向採用 TCB,預計亦將不利 Shibaura 短期 bonder 業績

Intel 需求主導 ASMPT TC Bonder 銷量與發展,隨著 Intel 採購需求停滯,ASMPT 於 TC Bonder 市占率變相下滑

綜合以上,投資人在評估相關業者先進封裝 Bonder 展望時,大客戶影響力更勝於景氣變化,應優先關注大客戶之間市占率競合 (台積電 vs Intel,海力士 vs 三星),以及大客戶自身技術路線圖變化 (例如台積電由 flip-chip bonding 轉向 TC bonding)。

Bonder 產業未來機會與風險

展望未來,不同 Bonder 市場將迎來不同的機會與風險。

Wire bonder:關稅削弱短期需求,長期關注垂直導線封裝機會

Wire bonder 作為傳統封裝主流應用,受總體經濟影響最為直接。整體產值在疫情達高峰後雖已連續三年下滑,但近期川普關稅政策激進反覆,將不利消費、車用、工業需求,近一步造成整體下游客戶短期資本支出縮手,使得 Wire bonder 落底復甦時間再延遲。

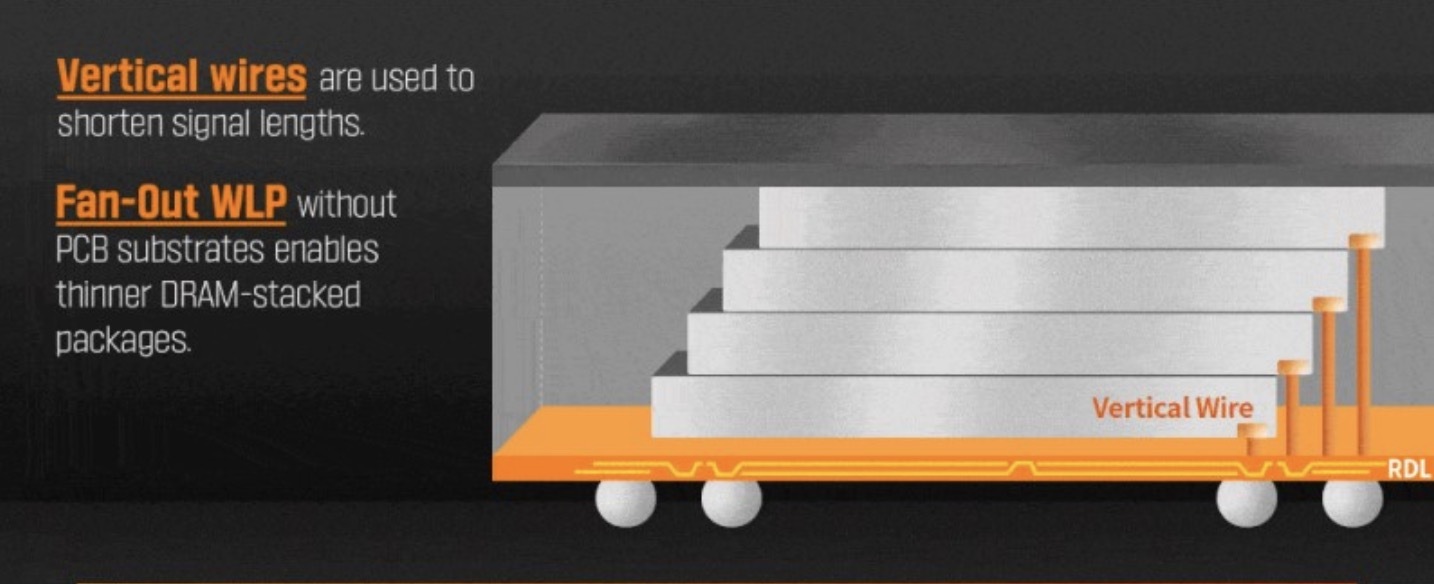

儘管 Wire bonding 技術已經成熟,但業界仍持續探索新的市場應用機會,其中垂直導線封裝技術 (vertical wire bonding) 值得期待。為了將 HBM 高頻寬性能引入手機裝置,海力士透過將 Fan-out 封裝和垂直導線封裝技術結合,推出名為 VFO (Vertical Fan Out) DRAM 產品,三星亦推出類似技術的 VWB/VCS 產品展示。Vertical wire bonding 仍處於早期驗證與測試階段,但考量 Eadge AI 需求快速成長可能縮短新技術導入時程,個人預期 27~28 年垂直導線封裝技術有機會商業化。

Flip Chip bonder:關稅削弱短期需求,下一代 InFO 技術為新成長機會

Flip Chip bonder 不小市場比重來自於傳統封裝,因此同樣受川普關稅政策衝擊甚深;而過去幾年受惠於台積電 CoWoS 採用 Flip Chip 而高速擴產的先進封裝市場,將因後續 CoWoS-L 轉向採用 Fluxless TC bonding 而成長受阻,以上兩因素可能使得 Flip Chip bonder 25~26 年需求偏向低迷。

然而展望 26 年後續,個人預期 Apple 於 iPhone A20 處理器導入下一代進化版 InFO 封裝 (市場目前稱呼為 WMCM) 將帶來重回成長契機。相較於目前的 InFO-POP 封裝中 DRAM 與處理器晶片垂直堆疊,下一代 InFO 將轉向 DRAM 與處理器水平放置於 RDL 之上,這將使得封裝流程中晶片與 RDL 接合需要額外 bonding 步驟。台積電 WMCM 封裝估計採用 Flip Chip bonding,考量 iPhone 手機晶片年銷量約在 2 億顆規模,下一代 InFO 封裝對 Flip Chip bonder 需求上升將逐步抵銷 CoWoS 需求下滑,個人估計 27 年 Flip Chip bonder 銷量有望再度向上。

TC Bonder:CoWoS-L 與 HBM4 將持續推動 25~27 年產值高速成長

儘管 TC Bonder 銷量與產值於 22~24 年已經數倍擴張,但展望 25~27 年個人預期成長動能仍有望延續:

由於半導體標準化組織 JEDEC 將 HBM4 厚度標準從之前的 720 μm 放寬至 775 μm,大幅減緩 HBM 導入 Hybrid bonding 的急迫性,使得既有 HBM 業者將持續採用成本較低的 TC Bonder,TC Bonder 仍將持續受惠後續 HBM4/4E 記憶體需求上升

台積電將於 NVIDIA 下一代 通用運算 GPU 平台 - Rubin 持續採用 CoWoS-L 封裝,但其中 CoW 環節 bonding 步驟將由目前的 Flip-Chip 轉向採用 Fluxless TCB,這將顯著擴大邏輯先進封裝市場對 TC Bonder 需求量,有效抵銷 Intel 對 TC Bonder 採購下滑。

然而 TC bonding 與 Hybrid bonding 存在部分替代競爭關係,考量:

HBM5 堆疊層數將近一步上升至 16~20 Hi,可能不得不導入 Hybrid bonding 以減緩晶片厚度增加,使得 TC Bonder 於 HBM 市場佔有率流失

隨著 AI 對運算需求高速上升,亦會加速通用運算 GPU/ASIC 對 IO 需求數量上升,推動 IO Pitch 近一步微縮,使得 Hybrid bonding 於邏輯先進封裝市場取代 TC Bonding 吸引力持續上升

個人認為自 28 年起,需關注 Hybrid bonding 於 HBM 和邏輯先進封裝市場是否開始替代 TC Bonder,削減 TC Bonder 成長速度。

Hybrid bonder:CPO、SoIC、晶背供電、HBM5 自 26 年起將接棒推動成長

相較於其他技術,Hybrid bonding 在 IO Pitch 微縮上具備優勢,但其整體高昂成本持續推遲下游導入時間,使得其於 25~26 年在 HBM4 和 CoWoS-L 導入的希望落空。而競爭技術 - TC bonding 持續推出 Fluxless 進化版本,使得其 IO Pitch 可進一步微縮至 15 μm - 甚至 10 μm 以內,仍有可能持續拖慢 Hybrid bonding 於部分市場導入速度。

然而導入速度減緩,並不代表無成長機會。自 26 年起受惠以下新應用採用,Hybrid bonder 銷量與產值仍有望加速成長:

NVIDIA 於下一代 Switch:Spectrum-X 與 Quantum-X 都將導入 CPO 技術,其中 EIC 和 PIC 採用 Hybrid bonding 垂直堆疊以提升光電轉換傳輸效率,估計將自 26 年推動 Hybrid bonder 需求上升

Apple 預計將於伺服器用 M5 Ultra 晶片導入台積電的 SoIC-mH 3D 封裝技術,有機會於 26 年推動 Hybrid bonder 需求上升

晶背供電 (Backside Power Delivery) 為推動邏輯先進製程於 2nm 以後持續微縮的關鍵技術,其必須採用 hybrid bonding 才能實現供電線路與晶圓對準接合。Intel 預計於 25 下半年預計將於 18A 製程開始導入,台積電則預計 26 下半年開始導入,預計將推動 Hybrid bonder 26 年需求上升

NVIDIA 預計於下下一代通用運算 GPU 平台 - Rubin Ultra 導入 CPO,若其中 EIC 和 PIC 持續研用 Hybrid bonding 垂直堆疊,將有望於 27 年推動 Hybrid bonder 需求進一步上升

HBM5 堆疊層數將近一步上升至 16~20 Hi,可能不得不導入 Hybrid bonding 以減緩晶片厚度增加,估計將自 27~28 年推動 Hybrid bonder 需求進一步上升

綜合以上,Hybrid Bonder 24~25 年雖受 TC Bonder 排擠而成長不如市場預期,但個人認為 26~28 年成長表現仍可期待。

相關供應鏈機會與風險

最後我們嘗試從 Bonder 產業未來展望,推估相關產業鏈上公司後續營運表現

庫力索法:Wire bonder 成長性低,Fluxless TCB 為短期成長亮點

K&S 庫力索法目前設備收入中超過 8 成來自於 Wire bonder,其主要應用市場 - 中低階消費、車用、工業需求築底尚未復甦下,卻又遭逢川普關稅短期進一步打擊,預期 25 年 Wire bonder 業務將持續低迷。

庫力索法 K&S 目前設備收入中雖然僅約 12~13% 來自於先進封裝,但個人預期 26~27 年有望加速擴張:

台積電後續 CoWoS-L 中 CoW 環節將採用庫力索法 Fluxless TCB bonder,公司目前已經開始小量交貨,預期 26~27 年將近一步擴大出貨量,數量級估計在 100 台

公司新開發的垂直導線封裝設備,可實現類 HBM 的 DRAM 堆疊封裝,但製造良率將優於目前以 TSV 堆疊封裝的 HBM,傳輸頻寬又可明顯高於既有 LPDDR,使得庫力索法的解決方案更適合於消費性 AI 應用中導入。公司預期 25 年對營收貢獻低於 0.2 億美元,但 26 年有望上升至 0.5 億美元,考量 Edge AI 趨勢將於未來幾年持續加速,個人看好 27~28 年此部分業務有望持續擴大

綜合以上,庫力索法雖然目前主要營收仍主要來自傳統打線封裝設備,個人預期 26~27 年其先進封裝設備收入將明顯擴大,帶動整體營收規模加速成長。

BESI:Hybrid bonder 預期 26 年起加速成長

BESI 貝思半導體營收近 8 成來自於 Die Attach/Bonder 相關設備,公司於 Die-to-Wafer Hybrid bonder 市占率估計近 80%,原本自身預估自 24 年起 Hybrid bonder 業務將大幅攀升,但後續實際銷量卻不如市場預期樂觀,個人估計主要原因在於 HBM4 與台積電 CoWoS 轉向採用 TC Bonder,而延後導入 Hybrid bonder 所致。

然而導入延後並不代表成長機會消失,展望 26~28 年個人估計 CPO、SoIC-mH、HBM5 等先進封裝應用將加速導入 Hybrid bonding,BESI Hybrid Bonder 業務於 26~28 年成長表現仍可期待。

ASMPT:大客戶 Intel 拖累短期營運,TCB、Hybrid bonder 追趕仍可關注

ASMPT 作為早期 TC Bonder 龍頭,但 23~25 年相關業務卻未能隨著整體 TC Bonder 產值走高而成長,反而市占率持續流失,個人估計原因在於:

Intel 過往為公司 TC Bonder 主要採購客戶,但近期營運不佳而減少支出,壓抑 ASMPT TC Bonder 短期成長動能

台積電於 CoWoS-L 的 CoW 環節將導入 Fluxless TC Bonder,但供貨目前由 K&S 率先拔得頭籌,ASMPT 能否切入供貨仍未知

海力士、三星於 HBM 轉向扶持韓國本土供應鏈,使得 ASMPT 無法享受近年 HBM 高速成長機會

儘管短期 ASMPT 先進封裝 Bonder 發展並不順利,但考量公司技術力強且相關市場需求持續高成長,ASMPT 未來幾年能否急起直追再度追趕擠進先進封裝大客戶供應之列,個人認為仍可關注:

儘管海力士 TC Bonder 主要供應業者為 Hanmi 韓美半導體,但在 24 年亦開始向 ASMPT 小量採購,未來公司於 HBM3E、HBM4 生產仍有機會成為海力士副供

台積電雖然目前已確認採購 K&S 的 Fluxless TC Bonder,但也仍在認證 ASMPT 機台,後續仍可關注 ASMPT 能否成為台積電 Fluxless TC Bonder 副供

ASMPT 過往在光通訊、矽光封裝領域處於領先地位,隨著 CPO 需求將於 26 年開始加速擴大,ASMPT 亦有機會利用其在光通訊封裝領域經驗切入大客戶供應鏈。

芝浦機電 Shibaura:CoWoS-L 市占率將流失,但下一代 InFO 將帶來重新成長機會

Shibaura 為台積電 Flip-Chip bonder 御用供應商,受惠於近年 AI 帶動 CoWoS 封裝高速成長,Shibaura 的 Flip-Chip bonder 業務為最大受益者。但隨著台積電 26 年起 CoWoS-L 轉向採用 TC Bonder,將使得 Shibaura 其在 CoWoS bonder 佔有率流失。

展望後續,個人預期 Apple 於 iPhone A20 處理器導入下一代進化版 InFO 封裝(市場目前稱呼為 WMCM) ,晶片與 RDL 鍵合將採用 flip chip bonding,考量 iPhone 手機晶片年銷量約在 2 億顆規模,下一代 InFO 封裝對 Flip Chip bonder 需求上升,將可逐步消化 CoWoS 需求下滑。考量 Shibaura 於台積電 Flip-Chip bonder 主要供應地位,其 Flip Chip bonder 業務有機會於 27 年後重返成長。