產業解析:面板級封裝 PLP 展望與競爭格局

前言

過去十年高階晶片市場以晶圓級封裝相關技術 - FOWLP、InFO、CoWoS、SoIC … 為主流,但隨著 AI 晶片封裝面積不斷膨脹,晶圓級封裝一次能處理晶片數量將明顯減少,其在大尺寸晶片封裝效率低落問題逐漸浮現。在 AI 晶片需求爆發下,在大尺寸晶片封裝效率更好的面板級封裝 (Panel Level Package) 估計將於 2026 起加速發展,成為未來十年中高晶片封裝技術主流之一。

(圖片來源:Yole)

基於以上,我們將透過兩篇文章和讀者簡介面板級封裝 PLP 展望與相關供應鏈,在本篇文章主要內容為:

前身:扇出晶圓級封裝 FOWLP 介紹

什麼是面板級封裝 PLP

面板級封裝 PLP 挑戰

面板級封裝 PLP 市場機會

面板級封裝 PLP 競爭格局

提及公司將包含:

OSAT 封裝測試:日月光 (3711)、力成 (6239)

晶圓製造:台積電 (2330)、Intel (INTC)、三星電子、意法半導體 (STM)

面板製造:群創 (3481)

玻璃載板:Absolics、三星電機、DNP 大日本印刷、欣興 (3037)

前身:扇出晶圓級封裝 FOWLP

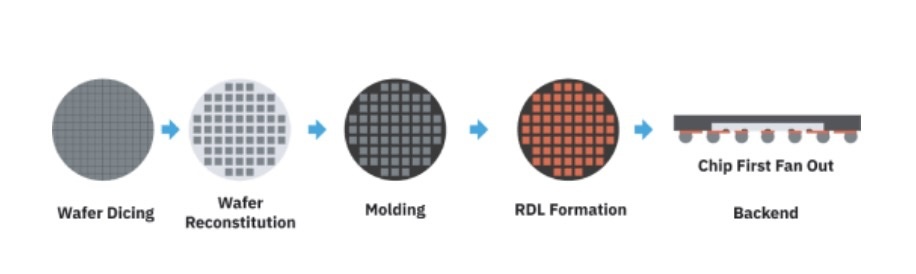

面板級封裝 PLP 並非憑空出現技術,而是基於扇出晶圓級封裝 FOWLP 技術衍生,並嘗試改善 FOWLP 瓶頸。兩者在製程、材料、設備都有高度重疊,因此先了解 FOWLP 可以對面板級封裝PLP 有更完整認識。

2010 年後手機、穿戴式裝置崛起,傳統主流 Flip Chip 覆晶封裝技術在相關應用有所侷限:

行動裝置晶片追求更小、更薄,但 Flip Chip 封裝中晶片仰賴錫球凸塊 bump 與載板連接,凸塊高度加上載板數百 μm 厚度使得晶片厚度難以降低

行動裝置追求訊號低耗損、低耗電,但 Flip Chip 封裝中訊號路徑需通過凸塊與厚載板內部銅走線,較長的路徑導致訊號耗損、能耗較高

行動裝置追求散熱,但 Flip Chip 中的載板核心材料為玻纖布與多層有機樹脂,材料本身散熱不佳且厚度厚,導致其散熱表現不佳

基於以上阻力,扇出晶圓級封裝 FOWLP 封裝技術因應而生

相較於 Flip Chip 中使用載板承載裸晶與形成晶片訊號傳輸路徑,FOWLP 改為採用更薄重分佈線層 RDL (Redistribution Layer) 取代載板,適合追求輕薄小的行動裝置晶片

FOWLP RDL 中銅走線線寬線距可以更小,使得 RDL 可以在更小面積形成銅佈線,銅佈線密度高於傳統載板,因此訊號耗損也更小

FOWLP 中裸晶採用更小的 microbump、甚至是無凸塊 bumpless 與 RDL 連接,不僅進一步降低封裝厚度,更短的訊號互連路徑也讓能耗、訊號表現也更佳

與載版結構類似,RDL 也是由一層一層的介電絕緣層與銅佈線堆疊形成。但 RDL 之所以能夠比載板更薄、內部銅線線距線寬可以更小更密、和晶粒鍵合可以無須凸塊,關鍵在於:

RDL 製程採用類前段晶圓製程,因此銅線距線寬可以更精細,在小面積中可容量更多佈線

RDL 成形、晶粒鍵合 (die bonding)、其餘封裝環節都整合在連續封裝流程中,而非傳統載板製造與封裝由不同獨立業者執行

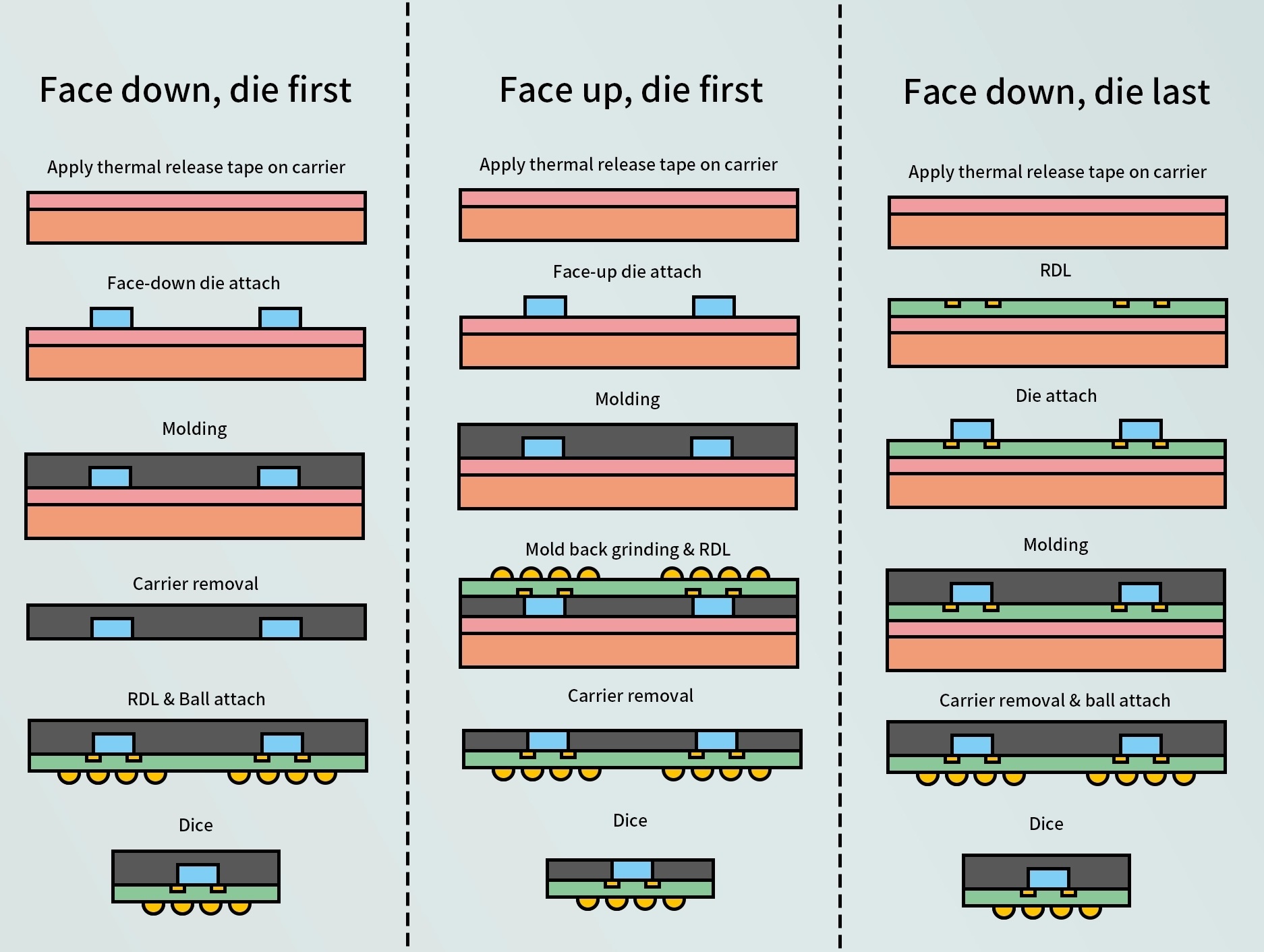

因此不同於傳統 Flip Chip 封裝流程中載板多為外購,RDL 形成本身就是 FOWLP 封裝流程中的關鍵步驟,且與前段晶圓製程有雷同之處:同樣都是在圓形晶圓載具上形成,並大量採用前段晶圓製程等級設備。根據 RDL 與裸晶鍵結順序不同,FOWLP 製程又可分為三種程序。

(圖片來源:Wiki)

Die-first Face-down:成本最低,但線寬線距難精細

簡化流程如下:

在圓形暫時載具上塗佈黏合劑,為後續晶粒排列放置作預備

將一顆顆晶粒正面 - 有 IO 腳位面朝下 (face down),排列放置在圓形載具上暫時黏合

在整片圓形載具上進行 molding 模封

移除圓形暫時載具,取下模封完成後的重構晶圓 (Reconstituted Wafer)

在重構晶圓上形成 RDL

植球並切割,完成封裝

(圖片來源:日月光)

Die-first Face-down 製程在三者中步驟最精簡,因此成本為三者中最低。但 Die-first Face-down 製程有兩個嚴重問題:

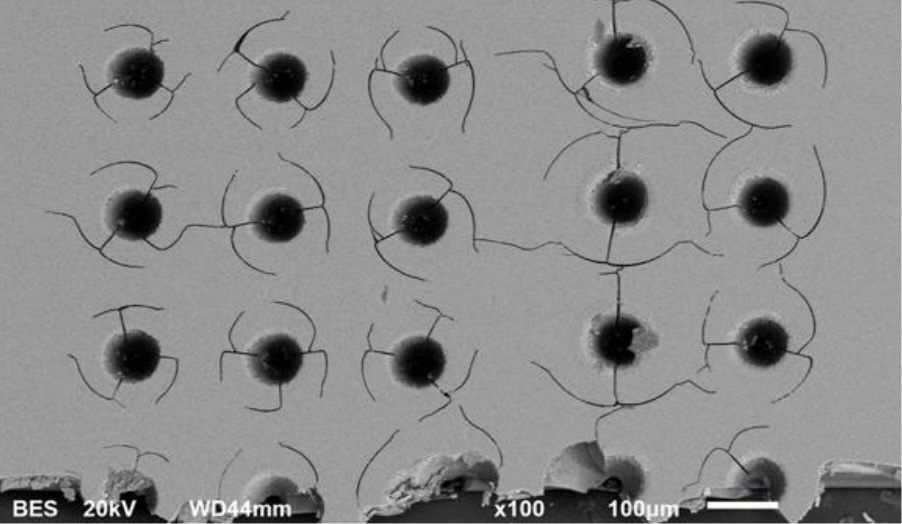

晶片位移 Die shift:晶粒、 molding 材料的熱膨脹係數不同,molding 環節加熱再冷卻過程兩者熱脹冷縮不一致,導致晶片位置會發生偏移現象

重構晶圓表面不平整:重構晶圓中晶粒表面與周圍的 Mold 交界處,也會有微米等級的段差

RDL 製程奠基在重構晶圓之上,重構晶圓上的晶片位移與不平整,使得後續曝光對準精度 (lithography overlay) 不精準,進而導致銅走線佈局與原先設計產生誤差。當銅佈線設計的線寬 / 線距越小,對此類對準誤差的容忍度就越低。這導致 Die-first Face-down 製程 RDL 銅走線線寬 / 線距多在 10/10~15/15 µm 等級,與高階載板差距不大,只能匹配 IO 腳位數量較少的低階晶片類型。

Die-first Face-up:線寬線距較精細,成本較高

簡化流程可參考上圖中間:

晶粒在前段製程時於 IO 腳位會先長出具有一定高度、較粗銅柱 Cu Pillar

在圓形載具上塗佈黏合劑,為後續晶粒重新排列放置作預備

將一顆顆晶粒 IO 腳位面朝上 (face up),重新排列放置在支撐用圓形載具上黏合

整片圓形載具進行 molding 模封

對於模封後的重構晶圓進行研磨 Grinding,讓晶粒 IO 腳位銅柱露出

在研磨後的重構晶圓上形成 RDL

移除支撐用圓形載具,取下 RDL 製程後的重構晶圓

植球並切割,完成封裝

為了應對降低晶片位移 Die shift 與重構晶圓表面不平整問題,Die-first Face-up 製程進行以下改進

Face up 代表是裸晶背面和圓形載具貼合,因此可以採用黏性極強的晶片黏合膠,降低後續晶片在圓形載具上因熱脹冷縮產生的水平位移,也不用擔心後續重構晶圓從載具取下時殘膠損毀 IO 腳位所在的裸晶正面

研磨步驟降低重構晶圓表現不平整

研磨會將晶片正面上多餘 molding 樹脂磨掉,直到 IO 腳位銅柱頂端露出來,而較粗的銅柱面積使得後續曝光對準較容易,進而降低晶片位移帶來的風險

基於以上,Die-first Face-up 製程線寬 / 線距多在 5/5~10/10 µm 等級,較 Face-down 製程更為精細,因此可匹配 IO 腳位數量較多的中階晶片,例如智慧型手機應用處理器 AP、通訊晶片,台積電目前為 iPhone 晶片代工採用 InFO-POP 封裝技術,其基礎就是 Die-first Face-up 的 FOWLP。但 Die-first Face-up 缺點是封裝步驟較 Die-first Face-down 更多,因此成本也高於 Die-first Face-down。

RDL-first:線寬線距最精細,但成本最高

簡化流程可參考上圖右方:

先在支撐用圓形載具上形成 RDL

晶粒使用凸塊與 RDL 鍵合

在整片圓形載具進行 molding 模封

移除支撐用圓形載具,取得模封完成後的重構晶圓

植球並切割,完成封裝

考量晶片位移、重構晶圓表現不平整問題,多出自於 molding 環節熱脹冷縮,RDL-first 製程改為先進行對晶片位移敏感的 RDL 形成步驟,後續再進行晶片鍵合與 molding 模封,徹底改善晶片位移對 RDL 銅佈線帶來的誤差風險。這使得 RDL-first 製程線寬 / 線距可進一步縮小至 2/2~5/5 µm 等級,因此多用來匹配 IO 腳位密集的 HPC、AI、伺服器高階晶片。

RDL-first 雖然線寬線距可達最精細,但換來的代價是成本進一步上升

為了達到更精細線寬 / 線距、更高佈線密度,RDL-first 大量採用前段晶圓製程等級的設備,機台價格更為昂貴。

RDL-first 為了把晶片鍵合在 RDL 上,必須回頭採用微凸塊 micro bump,額外的凸塊形成、晶片對位鍵合、鍵合後底部間隙填充 (underfill),不僅增加更多材料成本,也拉長生產時間

因此以成本角度來看,RDL-first 製程成本多半高於 Die-first。

什麼是面板級封裝 PLP

面板級封裝 PLP 製程與扇出晶圓級封裝九成雷同,最大差異在於:扇出晶圓級封裝是奠基於圓形載具上進行封裝步驟;PLP 則是改為在方形玻璃面板載具上進行封裝步驟 (這也是面板級名稱由來)。改為方形載具有什麼好處呢?

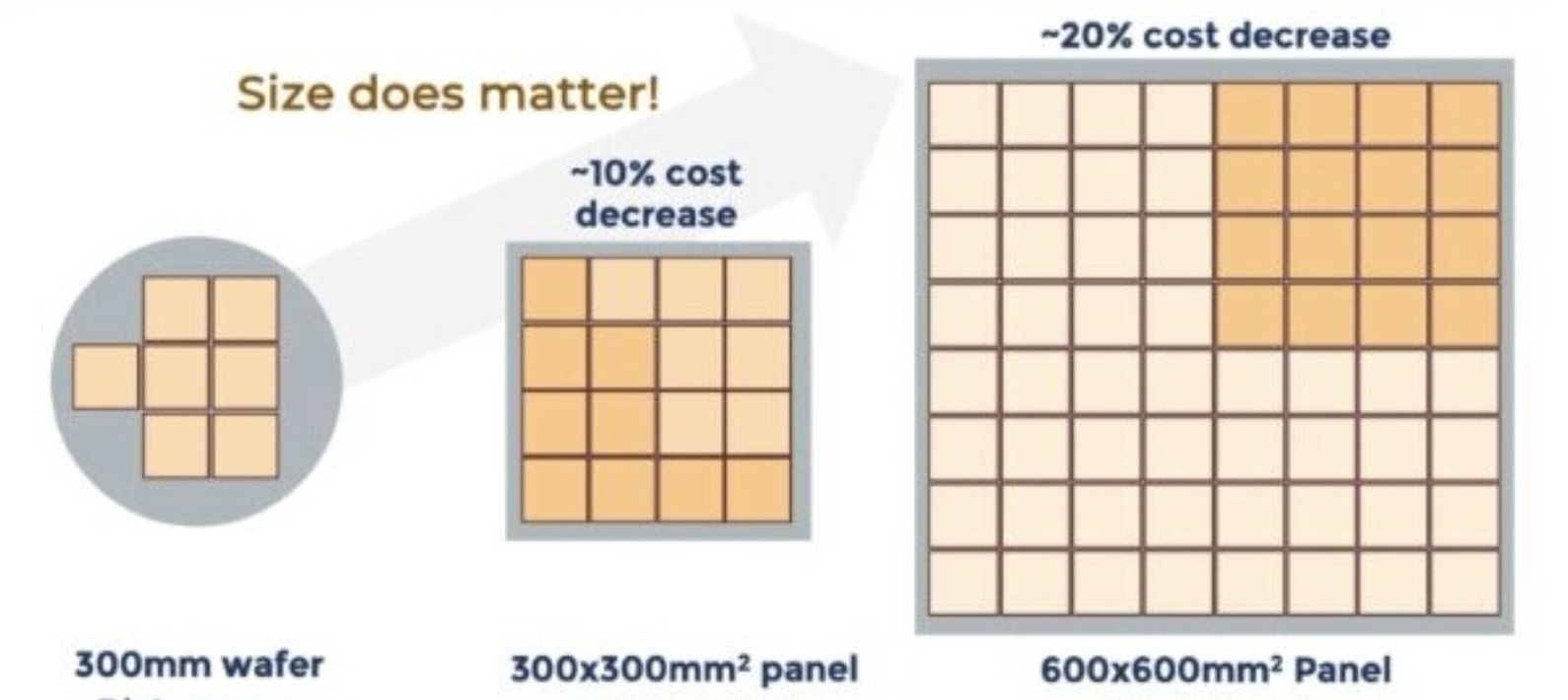

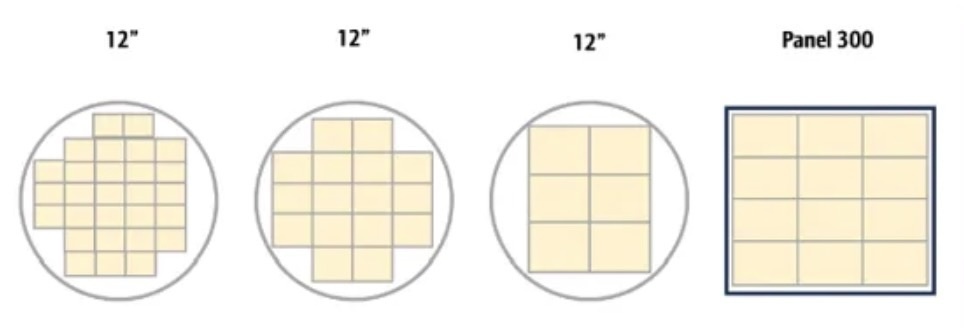

面積利用率更高,封裝產出效率提升

如前面所述,晶圓級封裝 FOWLP 製程與前段晶圓製程有雷同之處:同樣都是在圓形晶圓載具上形成,並大量採用前段晶圓製程等級設備,因此生產線與設備都是沿用晶圓製程思維。然而前段晶圓製程長期圍繞 12 吋 (直徑 300mm) 晶圓為基礎演進,這導致 FOWLP 載具也因此受限必須為 12 吋圓形大小,在其上放置排列方形晶片,邊緣部分面積勢必無法填滿,一次封裝可處理的晶片數量因此受到限制。

隨著 AI 晶片封裝面積不斷膨脹,圓形載具面積利用率低問題將明顯放大:

3.3 倍光罩尺寸大小晶片在 12 吋圓形載具能放約 18 顆,面積利用率約 70%

5.5 倍光罩尺寸大小晶片在 12 吋圓形載具只能放約 9 顆,面積利用率約 58.1%

9 倍光罩尺寸大小晶片在 12 吋圓形載具只能放約 4~5 顆,面積利用率約 42~53%

Nvidia 最新 Blackwell 晶片大小已經來到 2 倍光罩尺寸,未來朝 AI 運算晶片大小將持續往 8~9 倍光罩尺寸前進,採用 12 吋圓形載具面積利用將大幅下滑,封裝產出效率隨之明顯降低。面板級封裝 PLP 改為採用方形玻璃面板載具,與方形晶片在幾何尺寸上更容易配合,面積利用率將可較圓形載具提升。晶片尺寸越大,採用方形面板載具帶來產出效率提升就越明顯

(圖片來源:日月光,BofA)

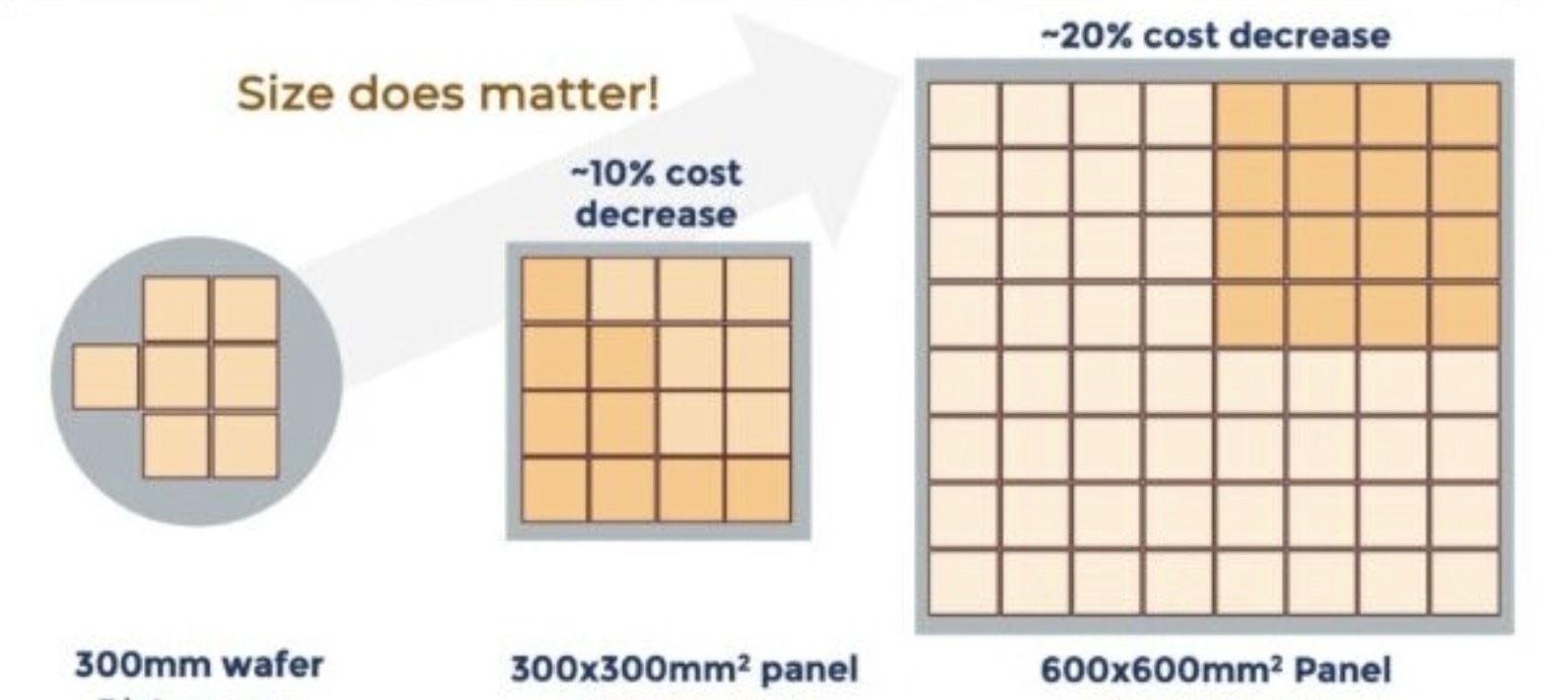

面積加大,封裝產出效率提升

面板級封裝 PLP 目標不僅是提高載具面積利用率,透過擴大玻璃面板載具尺寸,將可進一步大幅提高封裝產出效率。相較於 FOWLP 載具面積受制於 12 吋圓形晶圓,PLP 玻璃面板載具主流尺寸目前開始往 510x515~600x600 mm² 前進,未來甚至往 800x800mm² 邁進。更大面板載具尺寸將可放置更多晶片同時封裝,使得面板級封裝 PLP 理想產出效率與成本優勢遠遠高於 FOWLP。

(圖片來源:Yole)

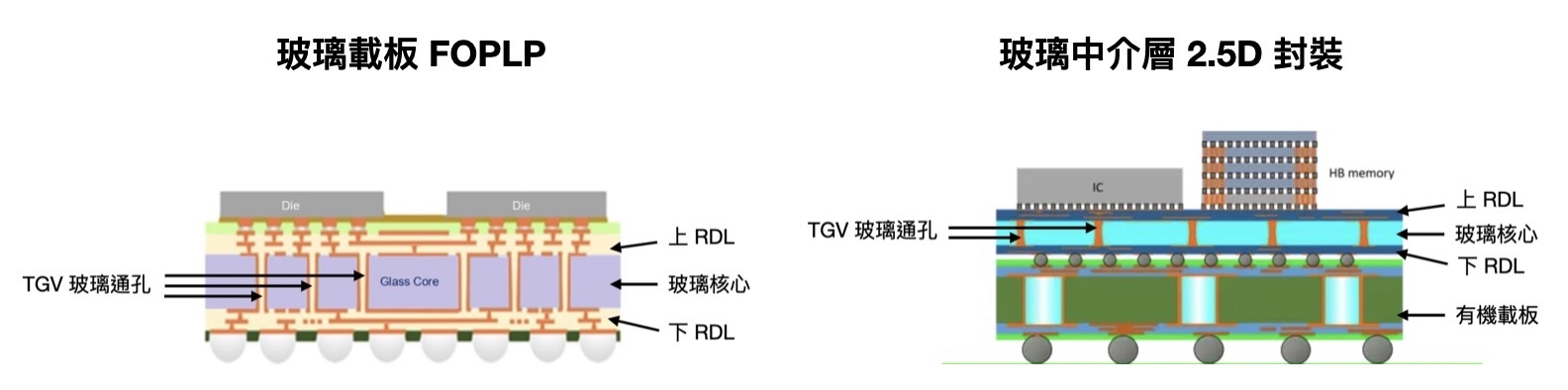

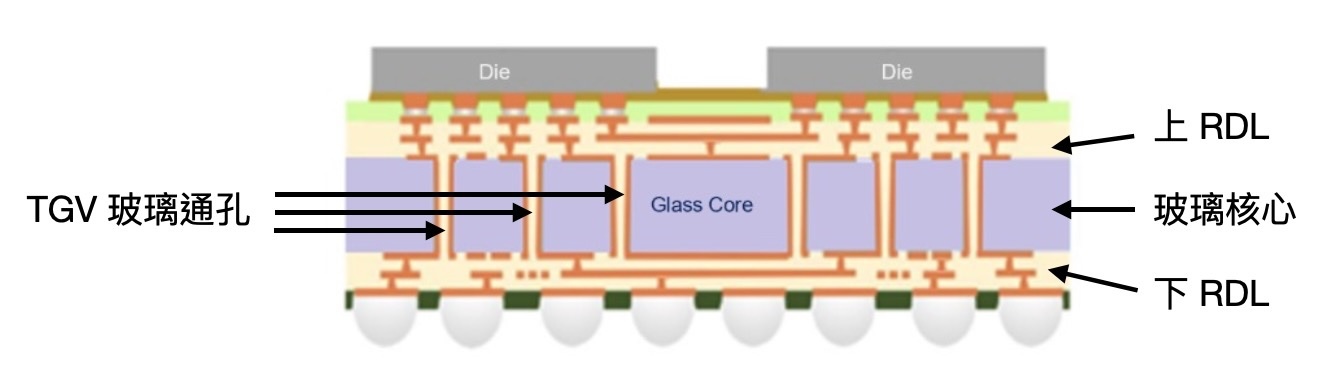

玻璃暫時載具轉向玻璃載板 / 玻璃中介層,提升性能

面板級封裝另一重要技術方向,不只是將方形玻璃面板作為 RDL 和晶粒的暫時載具,而是直接成為 RDL 的永久層核心材料。相較於純 RDL,加入玻璃核心帶來以下好處:

玻璃機械硬度更高,在製程搬運中不易變形

熱膨脹係數可透過配方客製化調整,降低高溫製程中翹曲風險

表面更平滑,其上可以堆疊更多層 RDL,互連密度越高

電損耗更低,更適合高頻信號傳輸以及光通訊

基於以上優點,在面板級封裝導入玻璃載板 / 玻璃中介層,為未來 AI、高性能運算晶片等高階應用重要技術方向。

(圖片來源:Intel、LPKF、財報狗整理)

綜合以上,面板級封裝 PLP 涵蓋兩種技術方向:

以大尺寸方形玻璃面板作為 RDL、晶粒的暫時載具,封裝結束不存在封裝晶片內

以大尺寸方形玻璃載板作為 RDL、晶粒的永久載具,封裝結束後永久存在於封裝晶片內

面板級封裝 PLP 挑戰

儘管面板級封裝產出效率理想上遠高於目前晶圓級封裝,但實際生產面臨不小障礙,使得過去 2025 年以前雷聲大雨點小,始終沒有進入大規模量產狀態。

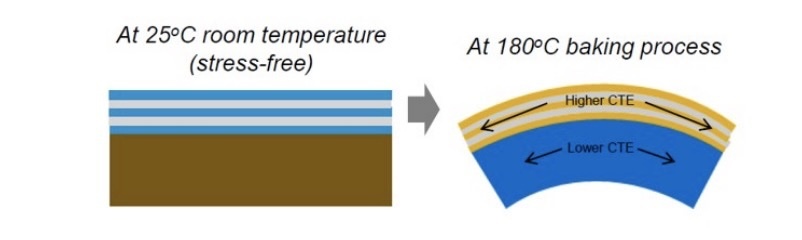

PLP 挑戰:Warpage 翹曲更嚴重

在未進行最後的切割步驟之前,載具上承載的重構晶圓 / 晶板是由裸晶、 molding 模封材料、RDL、銅線等異質材料所組成,不同元件、材料熱膨脹係數 (CTE) 差異巨大,在遭遇封裝流程中反覆加熱再冷卻步驟時,例如 molding 模封、RDL 中多次介電質 PI 成形 … 等,不同元件、材料膨脹和收縮幅度不一致,就會導致重構晶圓 / 晶板出現 Warpage 翹曲現象。

然而相較於晶圓級封裝,面板級封裝 PLP 遭遇 Warpage 翹曲問題更為嚴重:

晶圓級封裝採用圓形載具,在加熱冷卻過程中熱應力由中心到邊緣分佈是對稱且均勻的。但 PLP 採用方形載具,熱應力會明顯集中於四個直角處,這導致反覆冷熱循環時四個角落極易產生嚴重翹曲甚至龜裂。

微小的局部變形量,在晶圓級封裝 12 吋圓形尺寸還屬於可控範圍,但 PLP 所採用方形載板尺寸將擴大至 500x500mm 以上,更大面積會擴大變形效應,使得 Warpage 翹曲問題呈現指數級別的放大

嚴重的翹曲,會導致 RDL 銅線形成所需的曝光對準 (lithography overlay) 不準、裸晶鍵合位置偏差、銅線寬線距與開孔落點偏差 … 等多重問題,使得 PLP 封裝良率明顯降低。

(圖片來源:Corning)

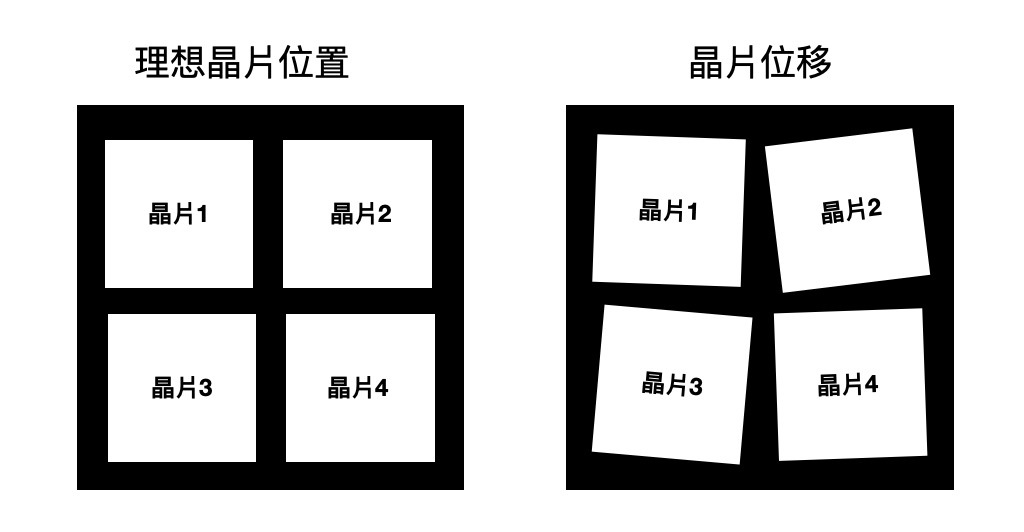

PLP 挑戰:Die shift 晶片位移嚴重

不同元件、材料熱膨脹係數不同,不只會造成 Warpage 翹曲問題,也是我們前面提到 Die-first 封裝流程會有晶片位移 Die shift 問題的主要元兇。然而相較於晶圓級封裝,面板級封裝 PLP 在晶片位移 Die shift 問題上更為嚴重:

如同在前面 Warpage 翹曲時的討論,更大載具面積會放大微小變形,因此也會造成晶片位移幅度在 PLP 明顯放大

PLP 翹曲問題嚴重,也會使得晶粒位置因曲面形變而被拉扯,進一步加劇晶片位移問題

Molding 模封步驟會先將顆粒狀的環氧塑封料 EMC 加熱成低黏度液態,再填入晶粒周圍空腔。液態 EMC 材料在載具上的流動會 “推動” 晶片位移,而更大載具面積會讓液態 EMC 在不同位置上流動更不平均,進一步加劇晶片位移問題

嚴重晶片位移 Die shift 導致晶粒的 I/O 焊墊 (與 RDL 銅線接合點位) 嚴重偏離預期位置,後續 RDL 曝光步驟若仍按照原先的標準光罩佈局進行曝光,銅線路就會無法精準連接到晶粒的焊墊上,導致電路斷路,使得 PLP 封裝良率明顯降低。

(圖片來源:財報狗)

PLP 挑戰:材料均勻難度高

RDL 是由一層一層的薄度僅微米級的介電絕緣層與銅佈線堆疊形成,在面板級封裝 PLP 製程中要讓這些材料在平面上均勻分布,難度比晶圓級封裝更高:

PLP 載具尺寸為晶圓級封裝的數倍,在更大的面積上要讓材料維持僅微米級薄度又要均勻分布,難度本來就更高

晶圓級封裝採用圓形載具,材料可透過成熟的旋轉塗佈技術,利用離心力液態材料能以極高的對稱性向外均勻延展。但 PLP 載具為方形,旋轉時四個角落更會產生嚴重的邊緣堆積效應,無法獲得均勻的厚度。業界轉向面板產業常用的狹縫塗佈 slit coating 技術,雖然適合大面積矩形,但在巨大尺寸載具上維持全版面僅數微米厚度的一致性仍極為困難,只要機台平台有微米的震動、狹縫模具的加工有些微公差,或液體材料流變性質有微小變化,就會有厚薄不均問題。

封裝過程材料成形往往需要進入烤箱進行烘烤固化 (Baking/Curing)。PLP 方形載具尺寸為晶圓級封裝載具的數倍,巨大方形在加熱盤上要維持極度嚴苛的溫度均勻性極為不易,一旦面板四角與中心的溫度不一致,膠材軟化程度就會不同,使得最後材料成形厚度不均勻。

RDL 金屬層與線路主要依賴濺鍍與電鍍等電化學沉積來完成。但根據電磁學原理,當導體或基板表面存在幾何上的尖銳特徵 - 例如方形面板的 90 度直角角落與直線邊緣時,電荷會自然地向這些區域高度集中。電流密度的不均勻,直接導致面板邊緣的金屬層或銅線路較厚

如同翹曲 Warpage 和晶片位移 Die shift,材料厚度不均導致重構晶板表面不平整,同樣會導致 RDL 銅線形成所需的曝光對準 (lithography overlay) 不準、裸晶鍵合位置偏差、銅線寬線距與開孔落點偏差 … 等多重問題,使得 PLP 封裝良率明顯降低。

PLP 挑戰:玻璃載板 / 玻璃中介層易碎難加工

要在面板級封裝近一步導入玻璃載板 / 玻璃中介層,雖然能換取不易變形、降低翹曲 warpage、互連密度上升等好處,但也會在製程中引入更多挑戰:

玻璃表面平滑不利於金屬材料附著,導入額外表面粗化步驟又可能生產新裂紋

玻璃通孔 TGV 為最難瓶頸,玻璃易碎導致通孔易產生裂紋 (cracks),

孔徑也難一致,導致金屬填孔時可能部分通孔空洞,或是通孔內銅體積不一致,將使得後續電阻與訊號表現不穩

由於玻璃載板相關製程難度過高,導入玻璃載板的面板級封裝技術仍處於研發試產階段,尚未進入量產商業化階段。

(圖片來源:LPKF)

面板級封裝 PLP 市場機會

由於前述製程挑戰,導致近年面板級封裝主要應用於中低階晶片市場,且量產規模有限。但隨著 AI 晶片需求爆發,面板級封裝近期發展有開始加速趨勢。

過往主力:以成本優勢滲透成熟製程晶片,Die-first FOPLP 為主

由於翹曲、晶片位移、材料不均勻問題嚴重,面板級封裝在精細銅線線寬線距良率不佳,因此 2020~2026 年面板級封裝主力市場以低銅佈線密度、低 IO 數類型晶片為主,例如電源 IC、射頻 IC、行動裝置處理器,採用封裝技術多為低成本的 Die-first FOPLP :

三星有實際量產技術為 Die-first FOPLP,應用於 2021 年發表的自家穿戴式裝置處理器Exynos W920,以及 2023~2024 年 Google 推出行動裝置處理器 Tensor G3/G4

力成 Die-first FOPLP 有小量出貨,估計應用於國內通訊晶片龍頭的 PMIC 封裝

群創目前量產技術為 Die-first FOPLP,客戶包含恩智浦和意法半導體的 Power IC 封裝訂單,以及 SpaceX 低軌衛星射頻 RF IC 封裝訂單

隨著技術與良率持續成熟,將帶動更多 FOPLP 量產導入穩定增加,中低階市場面板級封裝接受度也將持續提高,個人預期未來五年 Die-first FOPLP 在低成本市場將穩定擴大。

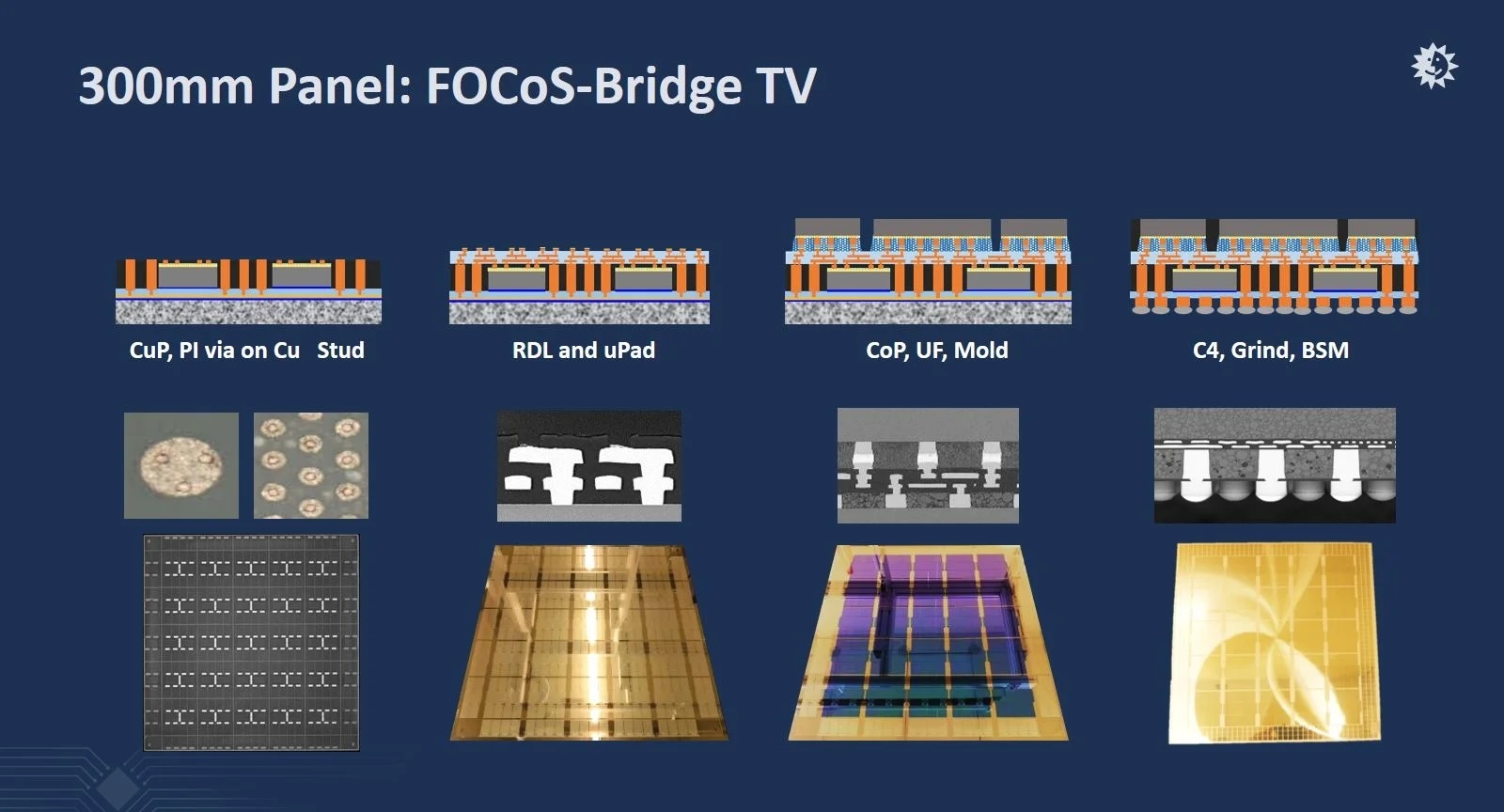

2026~2028 年:尺寸優勢滲透高效能運算晶片,RDL-first FOPLP、CoPoS 技術崛起

儘管面板級封裝過往主力為低成本中低階市場,但隨著 AI 高速運算晶片需求爆發,將有望成為面板級封裝未來加速發展的關鍵驅力。AI 應用追求低能耗、高速運算下,推動異質晶片從大面積的 PCB 版上互連,轉向整合於小面積的 RDL 上互連。然而隨著整合晶片越來越多,AI 晶片尺寸越來越大,晶圓級封裝採用的 12 吋圓形載具逐漸不符合使用

NVIDIA 2022~2023 年推出的 Hopper AI 晶片尺寸 814 mm²,封裝內整合 1 個運算晶片與 6 顆 HBM;但是到 2024 年 Blackwell 晶片尺寸擴大為 1600 mm²,封裝內整合 2 個運算晶片與 8 顆 HBM3e。2027 年 Rubin Ultra 晶片封裝內可能整合 2~4 個運算晶片與 8~12 個 HBM4,使得尺寸將再度擴大。

12 吋圓形載具上一次大約可進行約 27 個 Hopper 晶片封裝,但 Blackwell 將下滑至一次僅能進行約 14 個晶片封裝。隨著晶片尺寸加速擴大,12 吋圓形載具一次可封裝晶片數量、面積利用率都將快速下滑。

在 AI 晶片尺寸快速擴大的驅力下,將面板級封裝導入高效能運算需求加速浮現:

力成目前面板級封裝主力已提升至 510x510mm,近期宣布將投入 200 億台幣擴建 FOPLP 產線,共計月產能約 6 千片。其中一半產能設備預計 2026Q3 到位,另外一半產能設備則要到 2027 上半年才能到位。公司表示 FOPLP 全新產線瞄準 AI/HPC ASIC、CPU、連網晶片應用,估計短期潛在客戶可能為美系網通大廠。以設備到位時間推算,最快 2026 年底或 2027 年初可量產貢獻營收

日月光也預計尺寸 310x310mm FOPLP 全自動產線將於 2026 年底投產,另外會視客戶需求建制尺寸 620x620mm 產線

台積電目前主流的 2.5D 封裝技術 CoWoS-L,是以晶圓級封裝技術為基礎,在 12 吋圓形載具上形成由 RDL 和矽橋所組成的中介層。隨著 AI 晶片尺寸擴大,公司預計推出對應的面板級封裝技術 - CoPoS (Chip-on-Panel-on-Substrate),中介層改為在方形面板載具上進行製造,以提升封裝產出效率。目前估計 2026 年將透過子公司采鈺建制實驗產線,2026 年底~2027 年開始試產,但正式量產可能要等到 2028~2029 年後。

高效能運算晶片追求高密度佈線,估計將以能實現線距線寬 2/2 µm 等級的 RDL-first 製程為主,預期 2026~2028 年 RDL-first FOPLP 和 CoPoS 類似技術變體將加速興起。

2028~2030 年:面板級封裝採用玻璃載板 / 玻璃中介層有望商業化

玻璃載板 / 玻璃中介層技術難度最高,但在 AI 晶片持續追求更大封裝尺寸、更高互連密度、更低訊號損耗下,持續推進技術走向成熟:

玻璃載板廠 Absolics:玻璃載板 2024 年已開始小批量的試產與客戶送樣

載板廠三星電機:玻璃載板 pilot line 已建成,2025 年向客戶提供樣品進行推廣,目標是 2027 年量產

載板廠欣興:玻璃載板樣品驗證預期自 2026 年展開,目標 2027~2028 年量產

大日本印刷 DNP:玻璃載板 pilot line 2025 年底分階段啟動;2026 年初開始送樣;預計 2028 量產

Intel:2026 年初展示將玻璃載板導入自家 EMIB 先進封裝,預計 2030 年以前量產

以上來看,玻璃載板 / 玻璃中介層有望於 2027~2028 年進入量產下,採用玻璃玻璃載板 / 玻璃中介層的面板級封裝技術有望於 2028~2030 年將走向商業化。

面板級封裝 PLP 競爭格局

面板級封裝 PLP 融合了半導體前段製程與面板生產技術,這使得競爭戰場不再侷限於傳統的封測廠OSAT,更將晶圓代工廠與面板廠全數捲入其中。

封測業者 OSAT

封測廠商 OSAT 在封裝測試領域深厚底子,使其在面板級封裝自然具備多重優勢:

客戶關係先行優勢:封測業者龐大的 IC 設計客戶基礎,以及長期與客戶合作開發經驗,有助於其理解客戶導入面板級封裝痛點,推動客戶導入阻力較低

傳統封裝步驟能力強:面板級封裝仍然包含許多傳統封裝步驟 - Dicing 晶圓切割、Molding 模封、Die bonding 晶粒貼合、檢測,使得封測廠商在相關步驟經驗與能力強

傳統封測供應鏈優勢:面板級封裝部分步驟與傳統封測重疊,封測業者對於相關材料、設備供應鏈掌握度高,憑藉既有規模也有採購上成本優勢。

封測廠商在面板級封裝劣勢:

面板相關經驗與資本支出劣勢:不同於面板業者具備現成面板搬運、傳輸、大面積曝光顯影、大面積蝕刻的現成產線,封測業者產線與設備主要為 12 吋圓形晶圓設計,難以運用於面板級封裝產線。因此若要投入面板級封裝,傳統封測業者仍需投入產線全面汰換或升級鉅額資本。

晶圓製程設備資本支出劣勢:如同前面所述,面板級封裝繼承晶圓級封裝流程,因此也需大量採用前段晶圓製程等級設備。前段晶圓製程等級設備單價明顯高於傳統封裝設備,而封測業者規模明顯不如台積電、Intel、三星等晶圓製造巨頭,使得其在晶圓製程設備上有較高支出壓力。

類前段晶圓製程能力劣勢:若面板級封裝 PLP 未來驅力走向高效能運算晶片,高效能運算晶片封裝仰賴超高密度佈線,這將使得 PLP 加速導入更多類前段晶圓製造技術,且封裝與前段晶圓製程需共同設計優化,OSAT 業者在以上面向能力不如台積電、Intel、三星等晶圓製造巨頭,將成為其跨入高階面板級封裝市場的劣勢。

基於以上,低成本市場將面臨新進面板業者挑戰,高階市場上前段製程整合能力又難以和晶圓製造業者匹敵,個人估計封測業者主要優勢在於 5/5µm~10/10µm 中階市場。目前著墨於面板級封裝的傳統封測業者,又以力成、日月光投入最為明確。

力成:低、中、高階面板級封裝佈局最全面封測 OSAT

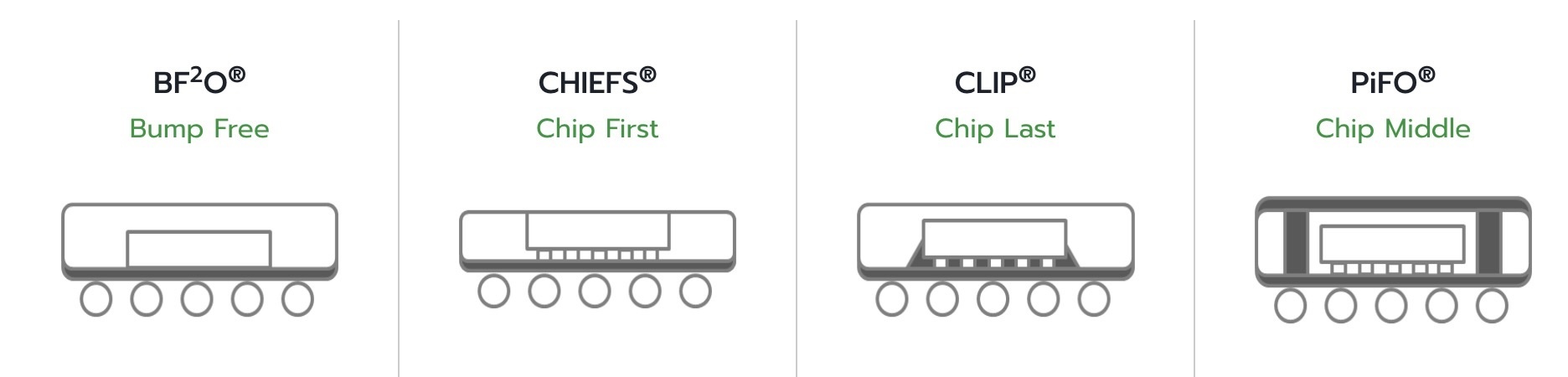

力成約在 2016 年開始布局 FOPLP,2019 年宣布進入量產,公司目前面板級封裝以 510×515 mm 尺寸為主力,提供技術類型有四:

BF²O:為 Die-first face-down FOPLP 技術,瞄準 RDL 銅走線線寬/線距大於 15/15µm 市場,例如PMIC、audio、PA 等應用

CHIEFS:為 Die-first face-up FOPLP 技術,瞄準 RDL 銅走線線寬/線距 ≥ 5/5µm 市場,例如手機 AP、基頻晶片、PMIC、記憶體應用

CLIP:為 RDL-first FOPLP 技術,瞄準 RDL 銅走線線寬/線距 ≥ 2/2µm 市場,例如 CPU、GPU、FPGA 等高階應用

PiFO:對標 CoPoS 技術,瞄準射頻模組、sensor、光學元件、SiP、3D 堆疊等高階應用

(圖片來源:力成官網)

以上顯示力成由 2/2µm~15/15µm、低階到高階面板級封裝應用皆有佈局,為目前檯面上發展面板級封裝最為積極、最全面的的傳統封測業者。

力成面板級封裝早期應用於 PMIC 等低階晶片 ,但近期公司在 FOPLP 產能開始加速擴建 :2025 年 11 月斥資69 億台幣收購友達竹科 3.5 代舊廠房,2026 年又再投入 200 億台幣新建 FOPLP 月產能約 6 千片,公司公告明確表示相關產能目的為因應 AI、HPC、車用電子需求,顯示力成面板級封裝已明確打入中高階應用。基於以上,力成估計短期將為面板級封裝受惠幅度最高的傳統封測業者。

日月光:310x310mm FOPLP 預計 2026 年底投產,瞄準高效能運算市場

日月光早在 2014 年即開始布局 PLP,2019 年正式宣布提供 FOPLP 封裝服務。官方目前將面板級封裝分為兩類:

310x310mm 方形面板:應用於 RDL-first 封裝流程,瞄準高密度佈線的 AI、高效能運算市場

620x620mm 方形面板:應用於 Die-first 封裝流程,瞄準低密度佈線低階市場

參考日月光近期法說會訊息,公司 2026 年將加速建置 310x310mm FOPLP 全自動產線,顯示公司可能接到高階應用潛在訂單,2026 年底投產後對於營運貢獻幅度可持續關注。

(圖片來源:日月光官網)

面板製造業者

面板製造業者憑藉在大、薄、方形面板製程豐富經驗,取得面板級封裝入場優勢:

大面板自動化搬運能力優勢:大面積、極薄且易碎玻璃載具在產線搬運上有易碎風險。面板廠本身就具備大尺寸玻璃基板上的自動化搬運、對位精度控制深厚經驗,在大尺寸載板 / 晶板傳輸與拿取系統建置能力較傳統封裝業者更強。

大面積曝光/圖形化經驗優勢:面板 TFT-LCD 的製造流程主要依賴曝光與顯影技術,這與 RDL 製造中銅佈線形成步驟有共通性,使得面板業者得以縮短在高線寬線距的 RDL 製程摸索時間。

大面積薄膜形成經驗優勢:面板的製造流程中包含大面積薄膜形成步驟,這與 RDL 製造中介電質、晶種層形成步驟有共通性,使得面板業者得以縮短在高線寬線距的 RDL 製程摸索時間。

閒置產能活化與折舊優勢:需求萎縮與對岸成本競爭壓力,台系面板業者在低階產能利用率本就偏低,將這些已經折舊殆盡的舊世代產線、設備、廠房轉為投入面板級封裝,將使得面板廠在早期成本較傳統封裝業者更有優勢。

但面板廠商在面板級封裝劣勢也很明顯:

客戶關係落後劣勢:面板業者為封測產業新進者,不僅缺乏成功案例可說服客戶,也缺乏長期與IC 設計客戶合作經驗,不利於與傳統封測業者爭取相同客戶訂單,打入新客戶供應鏈也需較長的試產磨合時間。

晶粒貼合精密度劣勢:面板級封裝仍然包含許多傳統封裝步驟 - Dicing 晶圓切割、Molding 模封、Die bonding 晶粒貼合、檢測,尤其 RDL-first 高階製程對於 Die bonding 晶粒貼合精度要求極高,面板業者缺乏傳統封裝步驟經驗,將使得其在 RDL-first 主導的中高階晶片市場處於劣勢

類前段晶圓製程能力劣勢:高效能運算晶片封裝仰賴超高密度佈線,需要導入更多類前段晶圓製造技術,且封裝與前段晶圓製程需共同設計優化,面板業者在以上面向能力不如台積電、Intel、三星等晶圓製造巨頭,將成為其跨入高階面板級封裝市場的劣勢。

基於以上,面板業者在面板級封裝具備低成本優勢,但在中高階市場上仍暫時落後領先封測廠、晶圓製造廠,個人估計其主要優勢在於 10/10µm~15/15µm 中低階市場。

群創:業界進度最快、已具備量產實績

群創是目前面板廠跨足 FOPLP 的絕對領頭羊,其利用已折舊完畢的 3.5 代產線打造業界最大尺寸 - 620x750mm 面板級封裝產線。公司目前在面板級封裝技術發展有三:

Die-first FOPLP 已於 2025Q2 量產,產量已從 400 萬顆爬升至近 4000 萬顆,目前產能處於滿載狀態,主要應用於恩智浦和意法半導體的 Power IC 封裝,以及 SpaceX 低軌衛星射頻 RFIC 封裝。

持續發展 RDL-first FOPLP,主要瞄準 AI、高效能運算等細線寬、高 I/O 的 chiplet 類封裝,但目前仍處於客戶認證階段

持續投入玻璃載板關鍵技術 - 玻璃通孔 TGV 研發,目前估計仍處於技術開發與客戶認證前期

Die-first FOPLP 量產爬升,證明群創在消費性、車用 PMIC、射頻晶片、音訊晶片 … 等低階面板級封裝市場具有潛力,唯獨目前貢獻營收比重仍非常低,要對獲利帶來明顯注意估計仍需數年發酵。

晶圓製造業者

如同晶圓級封裝,面板級封裝也導入類前段晶圓製程流程與設備,使得晶圓製造業者跨入高階面板級封裝具備天生潛力

類前段晶圓製程能力最強:高階面板級封裝追求超高密度佈線,會需要導入更多類前段晶圓製造技術與設備,且封裝與前段晶圓製程需共同設計優化,晶圓製造業者在前段製程能力明顯強勢

高階晶片客戶綁定優勢:5nm 以下先進晶圓製程掌握在台積電、三星、Intel 手中,先進晶圓製程業者可以透過其壟斷高階客戶先進製程優勢,順勢推銷搭售其後段封裝技術,這導致台積電在高階晶圓級封裝 (InFO)、2.5D 封裝 (CoWoS)、3D (SoIC) 封裝市占率極高,傳統封測業者在高階市場上只能承接台積電產能不足溢出的剩餘訂單。

晶圓製造業者雖然在高階市場具備潛力,但在面板級封裝發展仍有劣勢

面板處理經驗缺乏:不同於面板業者具備現成面板搬運、傳輸、大面積曝光顯影、大面積蝕刻的現成產線與經驗,晶圓製造業者產線與設備主要圍繞 12 吋圓形晶圓設計,因此缺乏大尺寸面板搬運、Warpage 翹曲優化、大面積材料均勻的處理經驗相對缺乏。

基於以上,儘管晶圓製造業者目前在面板級封裝腳步落後於封裝、面板業者,但在 AI 晶片尺寸快速擴展的趨勢下,估計未來晶圓製造業者將加速進入並主導 5/5µm 以下高階面板級封裝市場。

台積電:藉由 CoWoS 優勢順勢切入 CoPoS

透過在晶圓先進製程絕對領先綁定其封裝業務,台積電成為高階晶圓級封裝 (InFO)、2.5D 封裝 (CoWoS)、3D (SoIC) 封裝龍頭。儘管台積電目前還沒有提供面板級封裝 PLP 服務,但隨著大客戶 NVIDIA、AMD AI 運算晶片尺寸快速擴大,公司有極強驅力進入大尺寸高階 PLP 市場。

公司短期著墨面板級封裝技術為 CoWoS 的變體: CoPoS (Chip-on-Panel-on-Substrate),將中介層由圓形載具改為在方形面板載具上進行製造,以提升封裝產出效率;未來將近一步導入玻璃中介層。目前估計 2026 年將透過子公司采鈺建制實驗產線,2026 年底~2027 年開始試產,但正式量產可能要等到 2028~2029 年後。

三星電子:具備面板、載板、晶圓製程垂直整合優勢

在晶圓製造同業中,三星是唯一在面板級封裝有實際量產經驗的業者。如同前面所述,三星將其面板級封裝與晶圓代工服務搭售以吸引客戶:

2021 年發表的自家穿戴裝置處理器 Exynos W920,採用三星 5nm 製程與 Die-first FOPLP 封裝

2023~2024 年發表的 Google 行動裝置處理器 Tensor G3/G4 由三星代工,採用其 4nm 製程與 Die-first FOPLP 封裝

三星之所以在面板級封裝腳步較快,估計原因在於其本身就具備強大面板、載板製造經驗,使其在整合面板搬運、傳輸、大面積曝光顯影、大面積蝕刻流程具備先天優勢:

三星顯示器:具備大面積玻璃處理、生產經驗與玻璃中介層技術

三星電機:具備高階載板、玻璃載板量產與技術能力

三星 foundry:負責核心的半導體晶圓製造與高階封裝整合

因此在高階面板級封裝上,三星目前在關鍵的面板處理、玻璃核心製造上處於領先地位。

晶圓先進製程落後台積電為三星在高階面板級封裝主要劣勢。在台積電將領先的先進製程與自家封裝綁售強勢下,導致公司過往在高階先進封裝業務明顯落後。目前來看三星在 2nm 良率與產能持續落後,後續能否在高階面板級封裝市場扳回一城仍需觀察。

Intel:押注於玻璃基板技術

Intel 在面板級封裝強調的是玻璃材料直接導入,估計目前玻璃材料技術上領先其他晶圓製造業者。繼 2023 年 9 月宣布將推動玻璃載板技術後,2026 年 1 月又展示將玻璃載板導入自家 EMIB 先進封裝技術最新進展:

整體封裝尺寸達 78mm × 77mm,可支援兩倍光罩尺寸大小晶片封裝

玻璃載板中心為 2 層玻璃核心,上層 10 層 RDL 堆疊,形成 10-2-10 結構的厚載板

載板上層 RDL 中嵌入兩個矽橋晶片,作為多個晶粒訊號互通媒介

載板上晶片凸塊間距 Bump pitch 僅 45 μm,明顯小於 ABF 載板的 90~130 µm

Intel 強調測試時並未遇到任何玻璃碎裂問題,這顯示公司已克服玻璃通孔 TGV、玻璃切割製程上挑戰

公司目前先進封裝業務規模明顯不如台積電,但在 AI 晶片需求爆發、台積電先進封裝產能吃緊、美國政府要求半導體製造在地化等多重因素下,財務長表示近期先進封裝訂單已上升至每年數十億美元規模,其在大尺寸玻璃載板 / 面板級封裝市場發展仍值得關注。

(圖片來源:Intel)

意法半導體:與台積電、Intel、三星不在同一賽道上

作為功率、類比半導體 IDM / Fab-lite 大廠,意法半導體同時具備晶圓製造與封裝能力,且於 2015 年前就開始將類扇出晶圓級封裝的 eWLP 技術應用於射頻通訊晶片。2020 年起公司開始投入面板級封裝技術 PLP-DCI (Die-to-Copper Interconnect),特點為:

以 700x700mm 大尺寸面板取代 12 吋圓形載具,大幅提高生產效率降低成本

以銅柱取代傳統金線或錫球,顯著降低阻抗並提升散熱效率

支援異質整合,可將邏輯晶片、模擬元件與被動元件在單一封裝內

公司的 PLP-DCI 封裝技術已導入與 SpaceX 共同設計的射頻晶片,並於 2025 年在馬來西亞廠實現量產。基於第一條 PLP 產線成功經驗,意法半導體正加速推進下一代 PLP 技術,目標 2026Q3 於法國廠內小量試產。

不同於台積電、Intel、三星追求先進製程、高密度佈線、封裝尺寸擴大,意法半導體的車用、工業、通訊晶片多採用成熟製程,追求低功耗、散熱、小尺寸,因此其面板級封裝技術路線與市場估計和先進製程晶圓製造業者重疊度低,反而與傳統 OSAT 重疊度高。

但考量意法半導體主力產品 - 車用、工業晶片多為小量客製化類型產品,其面板級封裝將以滿足自家中高階晶片需求為主,不會與 OSAT 封測業者競爭量大的消費性市場,未來反而可能將中低階晶片委外採用 OSAT 業者的面板級封裝,以降低自建產能帶來的資金與成本壓力。因此未來在面板級封裝市場上,意法半導體與 OSAT 封測業者估計為互補而非競爭關係。

接下來 ...

本篇文章我們整理的面板級封裝 PLP 趨勢與主要業者,下一篇文章我們將為讀者解析面板級封裝材料和設備供應鏈。